# VPX3-215 3U VPX/VPX-REDI ExpressReach PMC/XMC Carrier Card

#### **Mezzanine Support**

- Single PMC/XMC site with PN1-PN6 connectors

- 64-bits of PMC I/O routed as per VITA 46.9

- Optional 24-bits of XMC I/O routed as per VITA 46.9

- High-performance XMC site supporting x8 PCI Express<sup>®</sup> (PCIe) link as per VITA 42.4

- PMC site supports up to 100MHz PCI-X

- PMC site supports both 3.3V and 5V PMCs

- PMC site supports 3.3V, 5V and +/- 12V power

- XMC site supports +5V and +/- 12V power

- I/O Configuration Two modes

- Mode 0 PMC and XMC I/O

- 64 signals of PMC I/O routed as per VITA 46.9 as 32 differential, impedance controlled pairs

- 24 signals of XMC I/O routed as per VITA 46.9 as 12 differential, impedance controlled pairs

- Two x4 lane PCIe ports routed as per VITA 46.4

- The two ports can be combined into a single x8 PCle port

**OpenVPX**

I/O consistent with VITA 46.9 option to allow common RTM module to be used for the VPX3-127 and Carrier I/O

Learn More Web / sales.cwcembedded.com Email / sales@cwcembedded.com

- Mode 1 PMC I/O with additional PCIe lanes

- 64 signals of PMC IO routed as per VITA 46.9 as 32 differential, impedance controlled pairs

- Four x4 lane PCIe ports routed as per VITA 46.4

- Two ports can be combined into a single x8 PCIe port

- I/O consistent with VITA46.9 option to allow common RTM module to be used for the VPX3-127 and carrier I/O

#### **PCI Express Switch Capability**

- Up to four x4 PCle ports routed from P1 providing access to PMC/XMC site or for switching between ports

- Ability to aggregate two of the P1 x4 lane PCIe ports to create single x8 lane port for higher bandwidth access to the XMC

## **Other Features**

- 3.3V and +5V operation

- Power management features

- Available in a range of ruggedization levels

- Air-cooled level 0 and 100, and conduction-cooled level 100 and 200 per VITA 46.0 (.8" pitch)

- Conduction-cooled per VITA 48.2, Type 1 card (.85" pitch with top and bottom covers, compatible with 1.0" pitch usage) upon customer request

- Utility Features

- The VPX3-215 drives the MRSTI# signal to each XMC for duration greater than 10msec from the time onboard power is stabilized in accordance with the VITA 42.0 specification

- User selectable option to drive the VITA 46 SYSRESET\* signal for a minimum of 10msec in response to an XMC reset from either XMC or a local VPX3-215 power-on reset

- Front Panel Indicator Provisions

- A red Fail LED is provided that can be set by the I2C bus, the default state is OFF

- A green LED is provided that goes on when all onboard power supplies are within specification

# Overview

Curtiss-Wright Controls Embedded Computing's VPX3-215 is one of a family of modules from Curtiss-Wright Controls to employ the new open architecture VITA 46 standard. VITA 46, also known as "VPX" was collaboratively developed by COTS industry leaders which included prime military integrators to marry high-speed serial interconnect such as Serial RapidIO<sup>®</sup> and PCI Express<sup>®</sup> (PCIe). It is well suited to the military/aerospace which can take advantage of and utilize this form factor and feature set in their demanding applications.

The VPX3-215 3U VPX ExpressReach carrier card is a member of the 3U VPX line of embedded ruggedized products. Designed to integrate with Curtiss-Wright Controls PCI mezzanine cards (PMCs), as well as other third party cards, this fully ruggedized carrier card, expands functionality of its host single board computer (SBC) by providing the ability to expand I/O capability without requiring additional SBCs as well as acting as a switch to switch data between up to four PCIe ports.

The VPX3-215 has been designed to handle both PMC and XMC mezzanine cards providing a host SBC to easily expanded its' I/O capability. To provide the flexibility required in today's application environments, the VPX3-215 comes in two I/O variants. The first provides a PMC/XMC site with 64 signals of PMC I/O mapped as 32 differential pairs, with 24 signals of XMC I/O mapped as 12 differential pairs, and two x4 lane PCle ports which can also be configured as a single x8 lane port. The second variant provides a PMC/XMC site with 64-bits of PMC I/O mapped as 32 differential pairs, and four x4 lane PCle ports which are connected to the on-board PCle switch and can be used to switch data between the ports.

# **VPX Module Format**

The Versatile Performance Switching (VPX) module format, governed by the VITA 46 specification and the associated VITA 48 Ruggedized Enhanced Design Implementation (REDI) was established to address the fundamental requirement to provide open-architecture modules that incorporate the high-speed serial interconnect technology that is becoming pervasive in high-performance computing.

The VPX standard was developed by the leading providers of COTS modules to address the major issue of high-speed serial interconnect, as well as incorporating numerous improvements learned after years of integrating VME and CompactPCI modules. The VPX standard, in short provides:

- 3U and 6U Eurocard form factors preserve chassis mechanical designs

- Support four x4 serial interfaces as the primary fabric

- Support of higher power modules and improved cooling

- Improved logistics with two-level maintenance and keying

The VPX module format provides many benefits to integrators of high-performance multiprocessor systems for radar, electro-optical and signal intelligence applications. PCIe functions as a fast connection between processors and the new generation of XMC modules which can easily be placed on VPX format carrier cards.

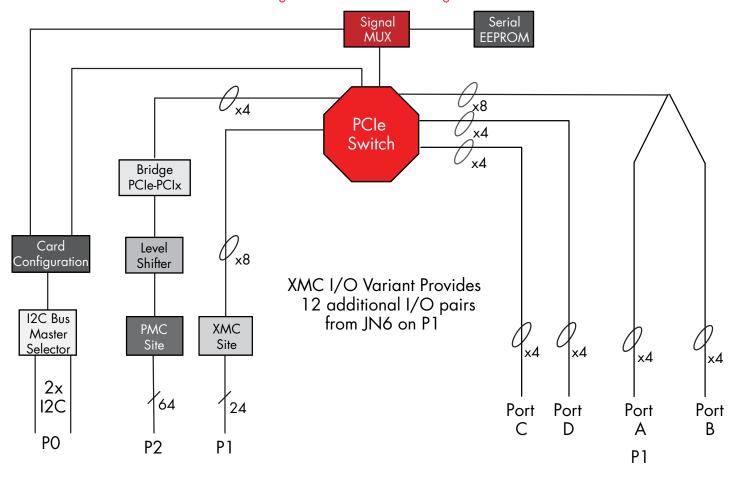

Figure 1: VPX3-215 Block Diagram

#### **Backplane Fabric Ports**

The VPX3-215 connects to other cards via up to four, 4-lane PCle ports thru the VITA 46 P1 connector (ports A, B, C, D). All PCle ports go through a PLX PEX8532 PCle switch.

The VPX3-215 is available in two configurations. The Mode O configuration, backplane ports A and B, can be selected to function as either two 4-lane PCle ports or as a single 8-lane upstream port. In the Mode 1 configuration, the VPX3-215 is accessed through four backplane 4-lane PCle ports, A,B,C & D. Ports A and B and be combined into a single 8-lane port via a user configurable jumper. Note that

there can only be one active upstream port. Any one port can be configured as an upstream port and the other(s) as a down stream ports to allow connections to other carriers in a chained manner.

Alternatively, the VPX3-215 can be built with a optional BOOT configuration EPROM which written to through the I2C interface. This is not a standard product offering, please contact factory.

## **XMC/PMC** Sites

The VPX3-215 is equipped with one mezzanine site capable of supporting a IEEE 1386 PMC or a VITA 42.3 XMC modules. The XMC site is connected to the PCIe switch through a 8-lane PCIe host interface on the Pn5 connector. The PMC is connected via a dedicated 4-lane port from the PCIe switch through PCIe to PCI-X bridge.

The VPX3-215 is available in two I/O variants. The I/O is mapped according to the VITA 46.9 draft specification which provides for controlled impedance, matched length differential pairs.

- Mode 0 64 signals of PMC I-O off PN4 is routed to the VPX P2 as 32 differential pairs. The 24 signals of XMC I-O off PN6 is routed to the P1 connector as 12 differential pairs. Two PCIe ports, A and B are provided.

- Mode 1 the 64 signals of PMC I-O off PN4 is routed to the VPX P2 as 32 differential pairs. The XMC PN6 signals are not routed to the backplane. Instead, these signals are used to provide two additional x4 lane PCIe ports - C and D, for a total of four PCIe ports (A, B, C, D).

On conduction-cooled cards, the XMC/PMC site adheres to the VITA 20- 2001 (R2005) Conduction-cooled PMC standard specifications. To optimize the thermal transfer from XMC/PMC modules to the basecard the standard VPX3-215 thermal frame incorporates both the primary and secondary thermal interfaces as defined by VITA 20-2001.

The VPX3-215 is capable of hosting processor PMCs in non-Monarch mode as described in the VITA 32-2003 draft standard (the Monarch# signal is left floating). The VPX3-215 does not support the optional second PCI agent, the optional EREADY signal, or the optional RESETOUT# signal.

Table 1: XMC/PMC site specifications provides details on the capability of the mezzanine site.

#### Table 1: XMC/PMC Site Specifications

| Function              | Site 1                                                                                                        |

|-----------------------|---------------------------------------------------------------------------------------------------------------|

| PCI interface         | PCI-X 64-bit 100MHz via 4-lane PCIe/PCI bridge                                                                |

| PCI Express interface | 8-lane per VITA 42.3<br>2GB/s peak simultaneous transmit and receive                                          |

| Pn4 I/O               | 64 signals (32 pairs) to VITA 46 P2 per VITA 46.9, pattern P64                                                |

| Pn6 I/O               | 24 signals (12 pairs) to VITA 46 P4 per VITA 46.9, , pattern x 12D                                            |

| Differential routing  | 100 Ohm differential, 50 Ohm nominal for both Pn4 and Pn6 I/O signals                                         |

| VIO                   | Jumper select for 3.3V or 5V                                                                                  |

| 3.3V power            | Provided from on-board PSU, 20W maximum to any one site. The 3.3V is sequenced with the main board power.     |

| 5.0V power            | Drawn from backplane 5.0V 30W maximum total. The 5V is sequenced with the main board power                    |

| 12V XMC Only          | Power for XMCs is selectable to be provided by backplane 5V or 12V through jumper selection. Max Power is 20W |

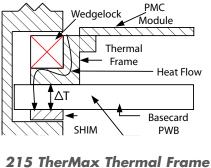

## TherMax-style Thermal Frame

A TherMax<sup>™</sup> thermal frame provides an unbroken metallic path from the PMC sites and shunted components to the back- side cooling surface of the card therefore minimizing the temperature rise to these devices. In comparison, a typical thermal frame simply sits on top of the PWB and forces heat to flow through the PWB which has a highthermal resistance compared to aluminum.

#### Figure 2: TherMax Diagram

A TherMax thermal frame eliminates the PWB heat rise inherent in a standard thermal frame

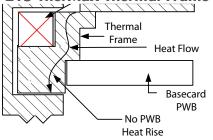

#### Full-width Thermal Interface to Back-side Slot Wall

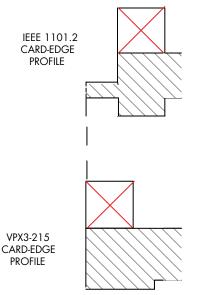

To minimize the temperature rise from the mating slot wall of conduction-cooled enclosures to the back-side thermal interface region of the VPX3-215, the VPX3-215 thermal frame maximizes the thermal interface area by extending the frame to the full width of the card, as illustrated in Figure 3. This deviation from the IEEE 1101.2 standard, which calls for the thermal frame to be notched for compatibility with card guides in standard air-cooled chassis, has the benefit of lower card operating temperatures and increased long-term reliability. During test and integration activities where it may be desirable to install a conduction-cooled VPX3-215 into an air-cooled card-cage, this can normally be accomplished simply by removing the card guides.

## Figure 3: Card-edge profile deviates from IEEE 1101.2

VPX3-215 Card-Edge Profile is Optimized to Provide a Fullwidth Thermal Interface to the Back-side Slot Wall

# **Status Indicators & Controls**

The VPX3-215 supports two front panel indicator LEDS. A red fail LED is provided that can be set via the I2C bus, the default state is OFF. A green LED is provided that goes on when all on-board power supplies are within specification. Should any of the on-board power supplies fail; the LED will not be lit.

Each PCIe lane for the backplane fabric ports and on-board PCIe ports (switch to XMC site and PCIe bridges PCI sites) has an indicator led that when lit indicates that the lane has been trained and is operational.

## 12C

The VPX3-215 has the ability to connect to two I2C interfaces from the backplane. Either I2C interface can be selected for control by an I2C master. Functions that can be controlled via the I2C interface are:

- Control the state of the red fail LED

- Reset the board

- Control the power state of the board (powered on or off)

- Read the state of the XMC, PMC present signals

- Control the selection of the upstream port of the 8532

- Read the XMC MBIST\_L signal

- Program the 8532 Configuration Boot ROM

## **Rear Transition Module**

The VPX3-215 makes use of cables and a rear-transition module (RTM) already developed for VPX3-127. To gain access to the backplane I/O signals of the VPX3-215, RTM3-127-000, is used. The RTM3 is a 3Ux81.5mm (VITA 46.10 compliant) module with a rear face plate and injector/ejector handles that plugs into the rear of the VPX backplane to make connections with the I/O signals emanating from the VPX3-215.

Refer to the VPX3-127 datasheet.

## **Specifications**

The tables below show the power, dimensions and weight characteristics of the card.

#### Table 2: VPX3-215 Power Requirements

| Voltage       | Current (A)            |

|---------------|------------------------|

| 3.3V          | 0.5A typ.<br>1.15A max |

| 5.0V          | 1.0A typ.<br>1.5A max  |

| 12V (VS1/VS2) | Used by XMC Only       |

| 12V Aux       | Not used               |

| -12V Aux      | Not used               |

#### Table 3: VPX3-215 Dimensions & Weight

| Option                   | Dimensions                       | Weight (grams) |

|--------------------------|----------------------------------|----------------|

| Air-cooled 1.0" option   | Per VITA 48 draft<br>1.0″ pitch  | 240            |

| Conduction-cooled        | Per VITA 46 draft<br>0.8″ pitch  | 285            |

| Conduction-cooled<br>LRM | Per VITA 48 draft<br>0.85″ pitch | 420            |

Note. The air-cooled format is designed to fit chassis with 0.8" slot pitch. For convenience it is shipped with a 1" front panel to accommodate installation in 1" pitch chassis.

Air-cooled cards available in temperature ranges 0 and 1.\* Conduction-cooled cards available in temperature ranges 1 and 2. Conduction cooled cards available in a covered, 2-level maintenance LRM configuration.

\* Refer to Ruggedization Guidelines data sheet for more information.

## Table 4: VPX3-215 Cooling Air Requirements

| Configuration               | Temperature Range | Air-Flow |

|-----------------------------|-------------------|----------|

| Stand alone with no PMC/XMC | -40°C to 71°C     | 10 CFM   |

Air-flow is specified for sea-level conditions. The temperature refers to the inlet temperature at the card. The air-flow specifications are for worst case (highest power) conditions, without any PMC/XMCs installed. Curtiss-Wright Controls can supply additional recommendations for specific power/temperature/altitude scenarios and pressure drop characteristics of the 215 support the design and testing of cooling subsystems.

# **Ruggedization Levels**

Air-cooled cards are available in levels 0, 100. Conductioncooled cards are available in levels 100 and 200 and a 2-level maintenance (LRM) configuration with ESD protective covers. See the Curtiss-Wright Controls ruggedization guidelines factsheet for more information.

Circuit card assembly is done to class 3 standards of IPC-A-610C, Acceptability of Electronic Assemblies. Standard conformal coating is acrylic PWB meets UL 94 V-0 flammability rating.

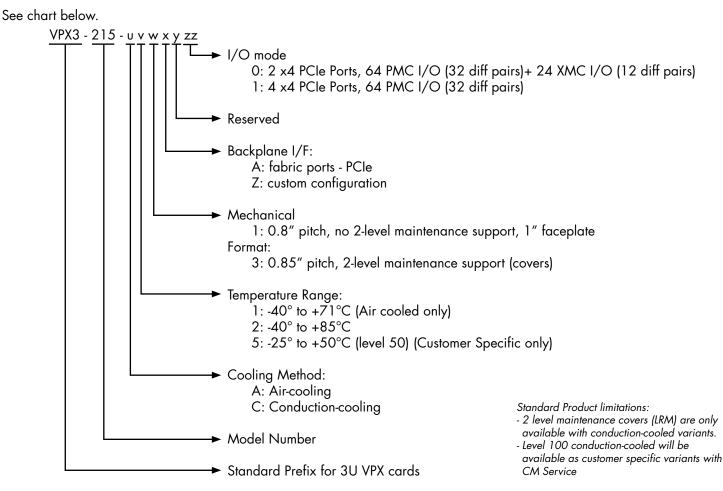

# **Ordering Information**

The VPX3-215 is ordered with the following part numbers.

# **Part Numbers**

# Warranty

This product has a one year warranty.

# **Contact Information**

To find your appropriate sales representative, please visit: Website: <u>www.cwcembedded.com/sales</u>

Email: <a href="mailto:sales@cwcembedded.com">sales@cwcembedded.com</a>

For technical support, please visit:

Website: <u>www.cwcembedded.com/support1</u> Email: <u>support1@cwcembedded.com</u> The information in this document is subject to change without notice and should not be construed as a commitment by Curtiss-Wright Controls Embedded Computing. While reasonable precautions have been taken, Curtiss-Wright Controls assumes no responsibility for any errors that may appear in this document. All products shown or mentioned are trademarks or registered trademarks of their respective owners.

7