VPX Intel<sup>®</sup> Core<sup>™</sup>2 Duo SP9300 Single Board Computer

### Features

#### Intel Core2 Duo SP9300 Processor

- 2.26 GHz

- 6 MB L2 Cache

- 1067 MHz FSB

- SSE4 floating-point libraries

#### Memory

- Up to 8 GB of DDR3 SDRAM

- 16 GB NAND flash

- 512 KB of NVRAM

- Memory bank DDR3 SDRAM up to 1066 MHz

#### I/O

- 2x PCle

- 2x GbE

- 2x RS-232

- 2x RS-422/485

- 3x USB 2.0

- 8x DIO

- 3x SATA

Learn More Web / sales.cwcembedded.com Email / sales@cwcembedded.com

### **IPMI and TPM**

- XMC site with eight lanes of PCIe

- IEEE 1386.1 Compliant

### **Operating System**

- Windows XPe

- VxWorks

- Linux

- LynxOS

### BIT

- BIT compliant with COTS Continuum features

- CBIT

- IBIT

- PBIT

### **Ruggedization Levels**

- Air-cooled

- Conduction-cooled

- Conduction-cooled VPX REDI LRM

### Introduction

Curtiss-Wright Controls Embedded Computing's (CWCEC's) VPX3-1252 combines the performance and the advanced I/O capabilities of Intel<sup>®</sup> Core<sup>™</sup>2 Duo SP9300 processor and Intel GS45 Chipset with an extensive I/O complement to provide a highly capable processing platform for a wide range of embedded harsh environment applications. Designed for space constrained applications, the VPX3-1252 represents the latest step in the evolution of rugged high-performance, highly integrated small form factor single board computers (SBCs). Available in a full range of environmental build grades, the VPX3-1252 is specifically designed to meet the challenges of rugged deployed high density computing. The VPX3-1252 packs the greatest functionality into the smallest standard form factor, draws the lowest possible power while retaining maximum flexibility, and offers an impressive complement of I/O capability to satisfy the most demanding harsh environment application needs.

The VPX3-1252 is designed to occupy a standard 0.8" slot and may be used for upgrading existing CompactPCI (CPCI) systems in the same footprint.

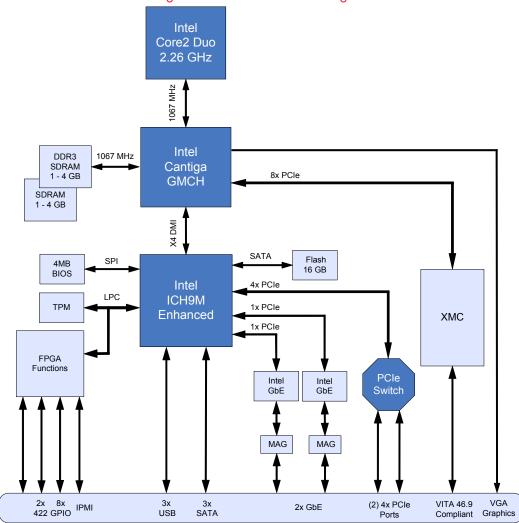

#### Figure 1: VPX3-1252 Block Diagram

The Versatile Performance Switching (VPX) module format is governed by the VITA 46 specification and the associated VITA 48 Ruggedized Enhanced Design Implementation (REDI). The VPX standard was established to address the fundamental requirement to provide open-architecture modules that incorporate the high-speed serial interconnect technology that is becoming pervasive in high performance computing. VPX was developed by the leading providers of commercial-off-the-shelf (COTS) modules to address the major issue of high-speed serial interconnects, while also incorporating numerous improvements resulting from years of integrating VME and cPCI modules. The VPX standard, in short provides:

- 3U and 6U Eurocard form factors preserve chassis mechanical designs

- Supports up to x4 serial interfaces as the primary fabric

- Supports up to 128 differential pairs in 6U format for modern high-speed interfaces such as DVI, SATA, SFPDP, SAS and custom sensor interfaces

- Support of VME for interoperability with legacy equipment

- Support of higher power modules and improved cooling

- Improved logistics with two-level maintenance and keying

The VPX module format provides many benefits to integrators of high-performance multi-processor systems for radar, electro-optical and signal intelligence applications. In particular Serial RapidIO<sup>®</sup> (SRIO) is suited to highbandwidth communications between processors in a VPX system, while PCI Express<sup>®</sup> (PCIe) functions as a fast connection between processors and the new generation of XMC modules which can easily be placed on VPX format carrier cards.

#### Overview

The VPX3-1252 is one of a family of modules from Curtiss-Wright to employ the new open-architecture VITA 46 standard. VITA 46, also known as "VPX", was collaboratively developed by prime integrators and other COTS industry leaders to marry high-speed serial interconnects such as PCIe. The VPX3-1252 provides SBC functionality to the Curtiss-Wright VPX family that includes quad-processor The VPX3-1252 is based on the Intel Core2 Duo SP9300 processor. Available with two processor cores with up to 4 GB of high-bandwidth DDR3 SDRAM, the VPX3-1252 provides high-performance processing, the massive 4GB/s bandwidth of VPX and a long list of features and I/O interfaces to satisfy the most demanding requirements of embedded computing.

The VPX3-1252 will occupy a standard 0.8" slot and may be used for upgrading existing CPCI systems in the same footprint. The VPX3-1252 is also available in the VITA 48 (VPX REDI) format with covers to support two level maintenance LRM requirements.

### **Powerful Intel SP9300 Dual-core Processing**

The SP9300 processor is based on Intel's industry-leading 45 nanometer (nm) High-k metal gate silicon technology and the latest microarchitecture enhancements. This next evolution in Intel Core microarchitecture builds on the tremendous success of the revolutionary microarchitecture (currently used in both the Intel<sup>®</sup> Xeon<sup>®</sup> and Intel Core2 processor families) and marks the next step in Intel's rapid cadence for delivering a new process technology with enhanced microarchitecture or an entirely new microarchitecture every year.

With more than 400 million transistors for dualcore processors, the 45 nm SP9300 introduces new microarchitecture features for greater performance at a 2.26 GHz, 6 MB L2 cache (which is 50% larger than most leading processors), and expanded power management capabilities for new levels of energy efficiency. The SP9300 family also includes nearly 50 new Intel SSE4 instructions for speeding up the performance of media and highperformance computing applications.

The table on page 4 illustrates the feature advancements of the Intel SP9300 processor and Intel GS45 Platform versus the Intel Core2 Duo 7520 MCH.

### Table 1: Feature advancements of the Intel SP9300 Processor and GS45 Platform versus the Intel Core2 Duo 7520 MCH

| Processor Features   | Core2 Duo 7520 MCH | SP9300   |

|----------------------|--------------------|----------|

| GS45 Number of Cores | 2                  | 2        |

| Core Frequency       | 1.5 GHz            | 2.26 GHz |

| L2 Shared Cache      | 4 MB               | 6 MB     |

| Front Side Bus (FSB) | 667 MHz            | 1067 MHz |

| Floating-point Unit  | SSE3+              | SSE4     |

| TDP (85%) Power      | 29 W               | 30 W     |

| Memory Bandwidth     | 6.4 GB/s           | 8.5 GB/s |

## **Power Consumption and CPU Tuning**

For applications requiring ultra low power consumption, the VPX3-1252 comes with a configurable BIOS capable of turning off one of the processing cores and providing the ability to adjust the processor core speed. The VPX3-1252 processing cores can be adjusted to run at two different speeds: 1.60 GHz and 2.26 GHz. In a low power consumption mode, the VPX3-1252 draws less than 30 W.

The following chart displays the VPX3-1252 power dissipation at different processor core settings while operating at 85°C:

### Table 2: Power Dissipation at 85°C

| Core Speed<br>(GHz) | Single-core<br>(Watts) | Dual-core<br>(Watts) | Typical<br>Board Power<br>(Dual-core<br>Watts) |

|---------------------|------------------------|----------------------|------------------------------------------------|

| 1.60                | 15.7                   | 19.0                 | 29.8                                           |

| 2.26                | 20.4                   | 26.3                 | 41.9                                           |

# **GS45** Northbridge

The VPX3-1252 employs the Intel GS45 Memory Controller Hub (GMCH) Northbridge. The comes equipped with an integrated video controller and handles the communication among the CPU, SDRAM, and the Southbridge. The GMCH manages the flow of this information by four main interfaces:

- 1066 MHz high-speed Front Side Bus (FSB)

- System Memory Interface (DDR3)

- Graphics Interfaces (DVI & RGB)

- Direct Media Interface (DMI)

### **ICH9M Southbridge**

The VPX3-1252 utilizes the Intel Controller Hub (ICH9M) Southbridge. The ICH9M controls the communication between the board's I/O and the Northbridge via DMI channels and a controller link. Some of the functions and capabilities of the ICH9M include:

- PCle\* Base Specification, Revision 1.1 support

- ACPI Power Management Logic Support, Revision 3.0b

### **Fabric Ports**

The VPX3-1252 provides two x4 PCIe ports to the backplane on all I/O modes, both implemented from PCIe within the Intel ICH9M. Both ports are routed to the P1 backplane connector and follow the pinout as defined by VITA 46.4. These interfaces can be used to interconnect VPX3-1252's together or to expand PMC/XMC capability using the VPX3-215 3U ExpressReach Carrier.

# **Dual SATA**

The VPX3-1252 provides three Serial ATA (SATA) 3.0 (3.0 GB/s) interfaces. Each interface incorporates several performance enhancing features such as:

- Independent DMA channel with 2K FIFO

- Independent command fetch, scatter/gather, and command executions

## XMC Site X8+12d24s VITA 46.9

The VPX3-1252 is equipped with one mezzanine site capable of supporting VITA 42.3 XMC modules. VPX standard by providing 24 single-ended and 20 pairs of differential I/O from the mezzanine site to the backplane connectors.

On the conduction-cooled card configuration, the XMC site adheres to the VITA 20-2001 (R2005) conduction-cooled PCI Mezzanine Card standard specifications. To optimize the thermal transfer form XMC modules to the base card the standard VPX3-1252 thermal frame incorporates both the primary and secondary thermal interfaces as defined by VITA 20-2001.

The VPX3-1252 utilizes the ICH9M which contains a Motorola MC146818A-compatible Real-time Clock (RTC) with 256-bytes of system supplied battery-backed RAM (the VPX3-1252 has no onboard battery). The RTC performs two key functions: keeping track of the time of day and storing system data, even when the system is powered down. The RTC operates on a 32.768 KHz crystal and a 3 V backplane or system supplied battery.

The RTC also supports two lockable memory ranges. By setting bits in the configuration space, two 8-byte ranges can be locked to read and write accesses. This prevents unauthorized reading of passwords or other system security information.

The RTC also supports a date alarm that allows for scheduling a wake up event up to 30 days in advance, rather than just 24 hours in advance.

### Software Support

### Continuum Software Architecture (CSA)

The VPX3-1252 is supported by a suite of firmware, RTOS board support packages (BSP), communication libraries and signal processing libraries. The Continuum Software Architecture is CWCEC's suite of firmware and BSP APIs that is common to SBC (VME, CPCI and VPX) and multiprocessor boards. Developers of mixed systems will find a common set of features and software interfaces for all future processing products from CWCEC. The Continuum Software Architecture is comprised of:

### **Continuum Firmware Monitor**

The monitor provides a command line interface over serial port or Ethernet to allow a user to perform a variety of system integration activities with the card. The monitor provides debug and display commands, diagnostic results display and exerciser controls, non-volatile memory programming and declassification and programming of parameters used to control boot-up and diagnostics.

Continuum Built-in Test (BIT) - a library of diagnostic routines to support Power-up BIT (PBIT), Initiated BIT (IBIT), and Continuous BIT (CBIT) designed to provide 95% fault coverage.

### **Operating System Software**

The VPX3-1252 is supported with an extensive array of software items, which cover all facets of developing application code for the board. Users have the option of choosing to develop with a variety of operating systems and development tools. The following operating systems are supported or planned for the VPX3-1252.

- VxWorks<sup>®</sup> 6.7 from CWCEC (part number DSW-1252-0670-VXW).

- Wind River<sup>®</sup> Linux<sup>®</sup> 3.0 BSP from CWCEC (part number DSW-1252-6300-LNX). The Linux BSP does not support the same level of BIT as does the VxWorks BSPs.

### **Continuum Vector Library**

Continuum Vector provides the user with a choice of APIs with support for the Vector Signal Image Processing Library (VSIPL, Core Lite) standard and the popular API established by Floating-point Systems Inc. See the Continuum Vector data sheet for detailed information.

### **Temperature Sensors**

The VPX3-1252 provides temperature sensors to measure board and processor temperatures. There is a sensor at each edge of the card and one sensor in close proximity to the processor. The sensors can be read by software and they can be configured to generate an interrupt in case of an over temperature condition.

### **Ruggedization Levels**

Air-cooled cards are available at Level 0 and Level 100. Conduction-cooled cards are available in Level 200 and 300 a 2-level maintenance (LRM) configuration with ESD protective covers.

- A/C

- L0 0.8" or 1.0" pitch

- LOO 0.8" or 1.0" pitch

- C/C

- L200 0.8" pitch

- L300 0.85" pitch

### Warranty

This product has a one year warranty.

### **Contact Information**

To find your appropriate sales representative: Website: <u>www.cwcembedded.com/sales</u> Email: sales@cwcembedded.com

# **Technical Support**

For technical support: Website: <u>www.cwcembedded.com/support1</u> Email: <u>support1@cwcembedded.com</u> The information in this document is subject to change without notice and should not be construed as a commitment by Curtiss-Wright Controls Embedded Computing. While reasonable precautions have been taken, Curtiss-Wright assumes no responsibility for any errors that may appear in this document. All products shown or mentioned are trademarks or registered trademarks of their respective owners.