MFC700 6U VPX-REDI 32GB Memory FPGA XMC Carrier with Serial RapidIO®

## **Applications**

- Image Processing

- Data Buffering

- Snapshot Recording

- Radar

#### Features

- Up to 32 GB DDR2 SDRAM with ECC

- Four x4 high-speed Serial RapidIO<sup>®</sup> (sRIO) links to the P1 VPX connector and low-speed I/Os to the backplane

- Onboard 8-port sRIO switch

- Dual Xilinx<sup>®</sup> Virtex<sup>®</sup>-5 LX110T FPGA memory controllers

- Additional RocketlO<sup>™</sup> connections between FPGAs and the backplane

- Air and conduction-cooled options, 1" pitch

- OpenVPX profile MOD6-PER-4F-12.3.1-n

## Overview

The MFC700 is a 6U OpenVPX compatible memory carrier with support for 16 GB of memory on the baseboard, dual XMC

mezzanine sites and a Serial RapidIO<sup>®</sup> (sRIO) fabric. Designed for applications that buffer large amount of high-speed data, the card can be utilized in signal and image processing applications, as well as snapshot and recording subsystems. The dual XMC mezzanine sites provide flexibility for system expansion, specifically for adding additional memory XMCs boosting the total memory capacity to 32 GB. With support for sRIO, the board can complement other Curtiss-Wright Controls Embedded Computing products such as the CHAMP-AV6/AV8, VPX6-185/187, HPE720, and VPX6-472.

Learn More Web / sales.cwcembedded.com Email / sales@cwcembedded.com

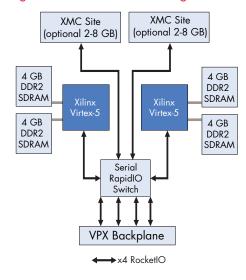

Figure 1: High-level MFC700 Block Diagram

The MFC700 is a large buffer memory board. Buffer memory sits as an endpoint on a fabric or bus, making it accessible to other resources such as FPGAs and processors. Uses of buffer memory include high-speed temporary storage, interleaving, data aggregation and warehousing, or providing additional system memory through a fabric. Buffer memory can act as a target or a master using a DMA engine.

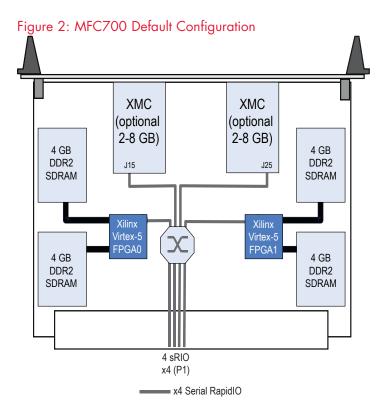

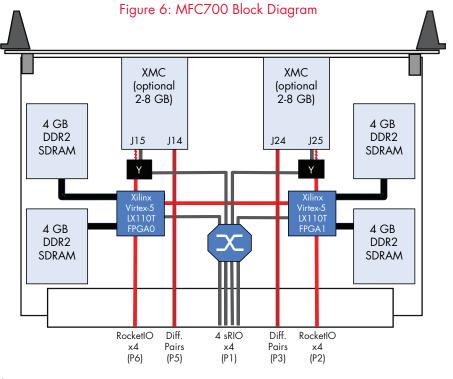

## Xilinx<sup>®</sup> Virtex<sup>®</sup>-5 FPGA Nodes

The FPGA nodes on the MFC700 combine large memory resources with a variety of I/Os for system needs. The FPGA nodes used on the board are Xilinx Virtex-5 FF1136 package FPGAs. The LX110T device is the default option for the board.

#### Memory

The FPGA's primary function is as a memory controller. Two large DDR2 SDRAM memory banks connect to each FPGA. Each bank is 72-bits wide with 64-bits for data and 8-bits for ECC. The standard configuration provides 8 GB per FPGA node. These banks run at 200 MHz, providing ample bandwidth for interconnects such as sRIO. Data can simultaneously be placed in one bank while DMA'd out of the other. This allows applications to take advantage of the full-duplex property of sRIO. By default, the board is supplied with a memory controller bit-stream that supports sRIO and does not support User Programmable Logic (UPL). Please contact the factory for applications that require user programming of the FPGA.

16 MB of flash for each FPGA node is available for storing bit-streams.

Figure 3: FPGA Memory and I/O Diagram

## Backplane I/O

Power Sub-system I2C & JTAG

from SCN

sRIO Switch

FPGA 1

#### Figure 4: Backplane connectivity

**VPX** Backplane

# PO x4 sRIO Ρ1 RocketIO x4 P2 32 Diff. Pairs or P3 J24 54 Sinale-ended 2 EIA-232 or SCN Ρ4 I EIA-232 with handshake 32 Diff. Pairs or J14 Ρ5 64 Single-ended RocketIO x4 P6 FPGA 2

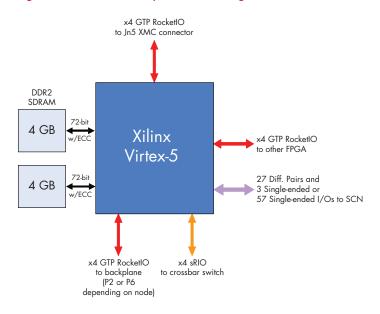

## FPGA I/O

The FPGA nodes provide access to the sRIO fabric, RocketIO and low-speed I/O to satisfy a variety of applications. The FPGAs use a 3.125 GB/s x4 link to connect to the sRIO switch. The FPGAs also include an advanced, corner-turning DMA engine, which is especially useful in matrix transposition, where converting from columns to rows can eliminate significant processor overhead. The sRIO switch links can be connected to other sRIO switches and endpoints, allowing the memory resources from the FPGA to be visible to all other parts of the system. The links support full-duplex transfers, enabling ping-pong transactions to the memory controllers or other I/Os of the device.

I/O capabilities for the FPGA nodes include RocketIO connections to the backplane, XMCs and between the FPGAs. A x4 link connects each FPGA to the backplane, using the P2 and P6 connectors. The RocketIOs can be used for protocols such as Aurora<sup>™</sup>, Serial FPDP (sFPDP) or other high-speed serial interconnects. RocketIO links between the FPGAs provide a low-overhead, high-speed connections where the FPGAs can compare data or do a transfer without going through sRIO.

#### **Mezzanine Sites**

The MFC700 includes two XMC (VITA 42) mezzanine sites. Each site can connect to the sRIO switch. This gives users the capability to access the sRIO fabric, specifically with the Curtiss-Wright MM-6171 Buffer Memory XMC module with up to 8 GB of memory. The MFC700 with two MM-6171s provides up to 32 GB of memory per slot (16 GB on the MFC700 baseboard and 8 GB per mezzanine site).

#### Figure 5: MM-6171 2-8 GB Buffer Memory XMC with sRIO

The mezzanines are also equipped with a Jn4 PMC connector, which can route up to 32 differential pairs or 64 single-ended I/Os to the backplane. These signals are routed from one mezzanine to the P3 VPX connector and the other to the P5 VPX connector.

#### Software

The MFC700 supports Wind River<sup>®</sup> VxWorks<sup>®</sup> 6.5 and Wind River<sup>®</sup> GPP Linux<sup>®</sup> 2.6.x. An API is provided for integration with other boards.

#### **Ruggedization Levels**

The MFC700 is supported with software drivers that run on SRIO-based VPX processor cards. VxWorks 6.x and Linux are supported. The MFC700 software is designed to also integrate with systems running the Curtiss Wright Inter-Processor Communications Library (IPC).

Serial RapidlO x4 HSS (RocketlO) x4, 3.125 Gbps Differential Pairs & Single-ended I/C Optional HSS (RocketlO) x4, 3.125 I/O Switch

#### Table 1: Specifications

| Table 1: Specifications                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Memory                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Sizes (Sum of all<br>four banks)       | 16 GB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Expansion<br>Memory (via XMC<br>sites) | 2-8 GB per site when using MM-6171 Buffer<br>Memory XMCs                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Bus Width per<br>Array                 | 72-bits wide (64-bit data and 8-bit ECC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Memory Array<br>Speed                  | 200 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| FPGA                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Device                                 | Xilinx Virtex-5 LX110T (consult factory for others)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| No. of FPGAs                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Connectivity                           | <ul> <li>x4 sRIO to each XMC connector</li> <li>x4 sRIO to switch</li> <li>x4 GTP RocketIO to backplane (P2 &amp; P6)</li> <li>x4 GTP RocketIO between FPGAs</li> </ul>                                                                                                                                                                                                                                                                                                                                          |  |

| Configuration                          | JTAG, off-board I/Os and onboard flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Mezzanine Sites                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| No. of Sites                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| XMC<br>VITA 42                         | Jn5 – supports sRIO x4 to switch by default                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| VPX<br>VITA 46.9                       | Jn4 – supports 64 single-ended signals or<br>32 differential pairs to P3 and P5                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Serial RapidIO                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Switch Device                          | Tundra Tsi578 8-port switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Connectivity                           | Both FPGAs, both XMCs, 4 connections to P1 fabric connector, all lanes at 3.125 GB/s                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Serial I/O                             | EIA-232 with handshake or<br>2 EIA-232s from SCN to P2                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Backplane                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Compliance                             | VPX (VITA 46) and VPX REDI (VITA 48)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Connectivity                           | <ul> <li>Power and SCN utility signals (I2C)</li> <li>4 sRIO x4s to switch</li> <li>RocketIO x4 from FPGA 1</li> <li>32 differential pairs or 64 single-ended I/Os from J24</li> <li>1 EIA-232 with handshake or 2 EIA-232s from SCN</li> <li>16 differential pairs or 32 single-ended I/Os from SCN</li> <li>32 differential pairs or 64 single-ended I/Os from J14</li> <li>1 x4 RocketIO link from FPGA 0</li> <li>16 differential pairs with 2 single-ended I/Os or 34 single-ended I/Os from SCN</li> </ul> |  |

| Software         |                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------|

| Operating System | Wind River VxWorks 6.x, Wind River Llnux                                                         |

| Standards        |                                                                                                  |

| Compliance       | VITA 20, 42.0, 42.2, 42.3, 46.0, 46.3, 46.9 and IEEE 1386                                        |

| Miscellaneous    |                                                                                                  |

| Power            | VPX<br>• 5 V<br>• +12 V                                                                          |

| Cabling          | JTAG cable and adapter (p/n JTAG-1001)                                                           |

| Weight           | <ul> <li>Air-cooled: 2.6 lbs (1.18 kg)</li> <li>Conduction-cooled: 3.21 lbs (1.45 kg)</li> </ul> |

#### Warranty

This product has a one year warranty.

## **Contact Information**

To find your appropriate sales representative: Website: <u>www.cwcembedded.com/sales</u> Email: <u>sales@cwcembedded.com</u>

# **Technical Support**

5

For technical support: Website: <u>www.cwcembedded.com/support1</u> Email: <u>support1@cwcembedded.com</u>

The information in this document is subject to change without notice and should not be construed as a commitment by Curtiss-Wright Controls Embedded Computing. While reasonable precautions have been taken, Curtiss-Wright assumes no responsibility for any errors that may appear in this document. All products shown or mentioned are trademarks or registered trademarks of their respective owners.