# ADC510 Dual-Channel 500/550 MSPS Analog Input FMC

# Applications

- Signal Intelligence (SIGINT)

- Electronic Counter Measures (ECM)

- Radar

#### Features

- Dual 500/550 MSPS 12-bit ADCs

- 1.5 GHz input bandwidth

- Onboard sample clock

- External clock input

- FMC/VITA 57 form factor

- Air- or conduction-cooled rugged versions

#### **Benefits**

- Direct ADC connection to host FPGA ensures maximum throughput

- Able to synchronize multiple channels/boards

- Easily interfaces to FPGA-based host board

- Complete ADC I/O

# Overview

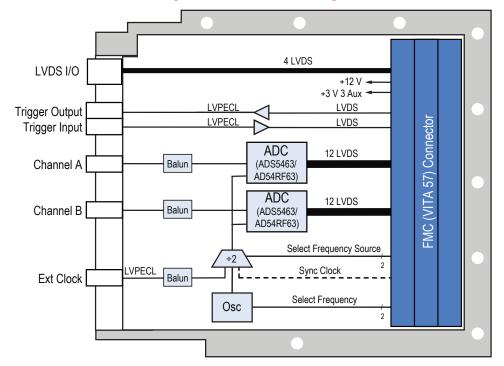

The ADC510 is a dual-channel 500/550 MSPS

analog input FPGA Mezzanine Card (FMC) based on the VITA 57 specification. This specification allows I/O devices to be directly coupled to a host FPGA. On the ADC510, the two ADC devices connect through the FMC site to an FPGA-based host board, maximizing data throughput and minimizing latency.

The ADC510 supports a choice of onboard sample clock frequencies as well as an external reference input. Multiple boards can be synchronized to increase the number of input channels. The ADC510 can be used on platforms like Curtiss-Wright Controls Embedded Computing's FPE650, a 6U quad Xilinx<sup>®</sup> Virtex<sup>®</sup>-5 FPGA VPX processor board.

# **Analog Input**

Two analog inputs are supported through  $50\Omega$  MMCX type front panel connectors. The analog inputs are singleended and are coupled to the ADCs using a balun and AC coupling capacitor configuration, in order to produce the broadband differential input required by the devices. The analog signal paths of both ADC inputs are matched to within 4ps to allow synchronous operation of the ADCs. The "Full Scale" analog input voltage is 2.2 Vpp (+11 dBm) at 1.5 GHz.

Learn More Web / sales.cwcembedded.com Email / sales@cwcembedded.com

#### **Clocks, Triggers & Synchronization**

An onboard oscillator is provided. The frequency can be selected by the carrier FPGA (through the FMC connector) for sample rates of 300, 320, 400 and 500 MSPS.

The external front panel clock input is through a  $50\Omega$  MMCX type front panel connector. The clock input is designed to operate at a typical frequency of 1.0 GHz but may operate at clock frequencies between 100 MHz and 1.1 GHz. The clock input may be sinusoidal or square, and is designed to operate with an input level between -2.0 dBm and +4.0 dBm. The analog sampling clock is derived from every 2nd rising edge of the input clock. It can be sourced from the carrier FPGA as part of the multi-board synchronization process.

Trigger In and Trigger Out use MMCX type front panel connectors. Actual functionality of these signals is dependent on the HDL code in the FPGA of the host carrier card. Trigger In is a single-ended LVPECL input signal. The maximum operating frequency of this input is designed to be approximately 300 MHz. Trigger Out is a single-ended LVPECL output signal. It is possible to synchronize the ADCs on multiple ADC510s using the Trigger In and Trigger Out signals. The ADC510 FusionXF HDK & SDK support this functionality.

The GPIO connector on the ADC510 is an ERNI dual row right-angle male connector, SMC Type B. Eight General Purpose Input/Output (GPIO) signals are split into four pairs, which are routed as loosely coupled pairs across the FMC.

#### FusionXF Software/HDL Support

Curtiss-Wright's FusionXF development kit includes software, HDL and utilities with examples and infrastructure for using the ADC510 on each supported host.

One of the core elements to the FusionXF development kit is a framework for adding new IP functionality or capabilities to the FPGA. It facilitates the inclusion of signal processing blocks such as digital down converters, making HDL development easier and integration more straightforward.

#### **Analog Performance**

The following figures provide data from Curtiss-Wright's preliminary analog characterization of the ADC510. They represent typical measured performance.

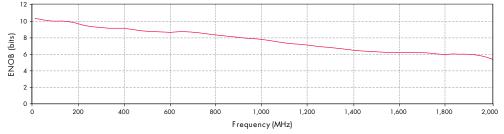

#### **Effective Number of Bits (ENOB)**

The ENOB is above 9-bits in the first Nyquist region. The board characteristics correlate to those of the ADC device over the frequency range shown.

#### Figure 1: ADC510 ENOB

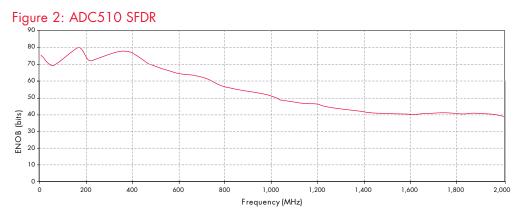

### Spurious-Free Dynamic Range (SFDR)

The SFDR is shown below. The main non-linear element in the ADC510 is the balun which performs the broadband singleended to differential signal conversion required for input to the ADC chip.

3

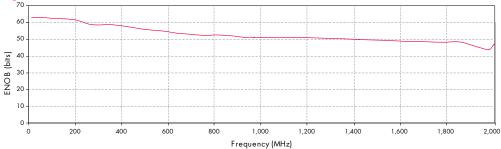

# Signal-to-Noise Ration (SNR)

The SNR correlates well to the ADC device.

#### Table 1: Board Specifications

| Analog Input             |                                                                                                               |  |  |  |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Number of Channels       | 2, single-ended                                                                                               |  |  |  |  |

| Sampling Frequency       | Up to 500 MSPS (550 MSPS with ADS54RF63)                                                                      |  |  |  |  |

| Full Scale Input Voltage | 2V2 pk-pk                                                                                                     |  |  |  |  |

| Device                   | 2x TI ADS5463 (or ADS54RF63)                                                                                  |  |  |  |  |

| Input Bandwidth (3dB)    | 1.5 GHz                                                                                                       |  |  |  |  |

| Input Impedance          | 50 Ohm, AC coupled                                                                                            |  |  |  |  |

| SNR                      | 58.94 @ 259 MHz                                                                                               |  |  |  |  |

| SFDR                     | 74.43 @ 259 MHz                                                                                               |  |  |  |  |

| ENOB                     | 9.47 @ 259 MHz                                                                                                |  |  |  |  |

| Clock & Trigger Inputs   |                                                                                                               |  |  |  |  |

| Clock Input Connector    | Front panel MMCX                                                                                              |  |  |  |  |

| Clock Input              | 50 Ohm, AC coupled LVPECL<br>-2.0 to +4.0 dBm input level (sine or square)                                    |  |  |  |  |

| Clock Input Frequency    | Sample rate is half input clock frequency<br>(i.e. 1 GHz for 500 MSPS)                                        |  |  |  |  |

| Internal Clock           | Selectable from:<br>• 600 MHz: 300 MSPS<br>• 640 MHz: 320 MSPS<br>• 800 MHz: 400 MSPS<br>• 1000 MHz: 500 MSPS |  |  |  |  |

| Trigger Input/Output     | Single-ended, 50 Ohm, LVPECL buffered to host FPGA                                                            |  |  |  |  |

| 2x yellow (host FPGA controlled)                                                                                                                 |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 4 differential pairs                                                                                                                             |  |  |  |  |  |

| Power Supplies                                                                                                                                   |  |  |  |  |  |

| 700 mA                                                                                                                                           |  |  |  |  |  |

| 200 mA                                                                                                                                           |  |  |  |  |  |

| 5 mA                                                                                                                                             |  |  |  |  |  |

| 2.5 V (+/- 5%) 250 mA                                                                                                                            |  |  |  |  |  |

| Software/HDL Code                                                                                                                                |  |  |  |  |  |

| FusionXF HDL support<br>(contact Curtiss-Wright for supported hosts)                                                                             |  |  |  |  |  |

|                                                                                                                                                  |  |  |  |  |  |

| <ul> <li>Air-cooled</li> <li>Air-cooled rugged</li> <li>Conduction-cooled</li> <li>RoHS compliant (contact factory for leaded builds)</li> </ul> |  |  |  |  |  |

|                                                                                                                                                  |  |  |  |  |  |

Note:

All the analog characterizations in this datasheet represent the measured performance of a standard production board in normal laboratory conditions. These are typical performance figures and are not guaranteed.

#### Table 2: Environment Specifications

| Table 2. Environment opeenteditons |                                                                  | Air-cooled                         |                                    |                                    | Conduction-cooled                 |                                   |

|------------------------------------|------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|-----------------------------------|-----------------------------------|

| Part number extension              |                                                                  | Level 0                            | Level 100                          | Level 200<br>(Note 6)              | Level 100                         | Level 200                         |

| Temperature                        | Operational<br>(Air-cooled Note 4)<br>(Conduction-cooled Note 7) | 0 to +50 °C                        | -40 to +71 ℃                       | -40 to +85 ℃                       | -40 to +71 ℃                      | -40 to +85 ℃                      |

|                                    | Non-operational (storage)                                        | -40 to +85 °C                      | -55 to +125 ℃                      | -55 to +125 ℃                      | -55 to +125 °C                    | -55 to +125 °C                    |

| Vibration                          | Sine (Note 1)                                                    | 2g peak<br>15-2k Hz                | 10g peak<br>15-2k Hz               | 10g peak<br>15-2k Hz               | 10g peak<br>15-2k Hz              | 10g peak<br>15-2k Hz              |

|                                    | Random (Note 2)                                                  | 0.01g <sup>2</sup> /Hz<br>15-2k Hz | 0.04g <sup>2</sup> /Hz<br>15-2k Hz | 0.04g <sup>2</sup> /Hz<br>15-2k Hz | 0.1g <sup>2</sup> /Hz<br>15-2k Hz | 0.1g <sup>2</sup> /Hz<br>15-2k Hz |

| Shock (Note 3)                     | Operational                                                      | 20g peak                           | 30g peak                           | 30g peak                           | 40g peak                          | 40g peak                          |

| Humidity                           | Operational                                                      | 0-95%<br>non-condensing            | 0-100%<br>non-condensing           | 0-100%<br>non-condensing           | 0-100%<br>non-condensing          | 0-100%<br>non-condensing          |

|                                    | Non-operational (storage)                                        | 0-95%<br>non-condensing            | 0-100%<br>condensing               | 0-100%<br>condensing               | 0-100%<br>condensing              | 0-100%<br>condensing              |

| Conformal Coat                     | (Note 5)                                                         | No                                 | Yes                                | Yes                                | Yes                               | Yes                               |

Notes:

1. Sine vibration based on a sine sweep duration of 10 minutes per axis in each of three mutually perpendicular axes. May be displacement limited from 15-44 Hz, depending on specific test equipment.

2. Random vibration 60 minutes per axis, in each of three mutually perpendicular axes.

Three hits in each axis, both directions, 1/2 sine and saw tooth. Total 36 hits.

Standard air-flow is 8 cfm at sea level. Some higher-powered products may require additional airflow. Consult the factory for details.

Conformal coating type is manufacturing site-specific. Consult the factory for details.

This is a non-standard product. Consult factory for availability.

7. Temperature is measured at the card edge.

Figure 4: ADC510 Block Diagram

# Warranty

This product has a one year warranty.

# **Contact Information**

To find your appropriate sales representative: Website: <u>www.cwcembedded.com/sales</u> Email: <u>sales@cwcembedded.com</u>

# **Technical Support**

For technical support: Website: <u>www.cwcembedded.com/support1</u> Email: <u>support1@cwcembedded.com</u>

The information in this document is subject to change without notice and should not be construed as a commitment by Curtiss-Wright Controls Embedded Computing. While reasonable precautions have been taken, Curtiss-Wright assumes no responsibility for any errors that may appear in this document. All products shown or mentioned are trademarks or registered trademarks of their respective owners.